Understanding The Verilog OR Gate: A Comprehensive Guide

The Verilog OR Gate is an essential component in digital design, forming a fundamental part of many electronic systems. This logic gate enables the creation of complex circuits by allowing multiple input signals to be combined into a single output. Understanding how to implement and utilize the Verilog OR gate is crucial for engineers and developers working in the fields of hardware design and digital systems. In this article, we will delve into the workings of the Verilog OR gate, its syntax, and practical applications, providing a comprehensive understanding of its role in digital logic design.

The ability to design circuits using hardware description languages (HDLs) like Verilog is of utmost importance in the electronic engineering domain. The Verilog OR gate serves not only as a basic building block but also as a gateway to understanding more complex digital systems. By mastering the OR gate, designers can apply this knowledge to create increasingly intricate logic circuits, enhancing their overall design capabilities. In this exploration, we will also cover the syntax used to define and implement the Verilog OR gate, along with examples to illustrate its functionality.

As we navigate through the intricacies of the Verilog OR gate, we will address common questions that arise among students and professionals alike. What are the key characteristics of the OR gate in Verilog? How can one effectively implement this gate in a digital circuit? By answering these questions, we aim to equip readers with the knowledge needed to leverage the Verilog OR gate within their own projects successfully.

Read also:Uncovering The Significance Of If My People Who Are Called

What is the Function of the Verilog OR Gate?

The Verilog OR gate is a fundamental digital logic gate that operates on binary inputs. It produces a high output (1) when at least one of its inputs is high (1). In essence, the OR gate can be described using the truth table below:

| Input A | Input B | Output (A OR B) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

How to Implement the Verilog OR Gate?

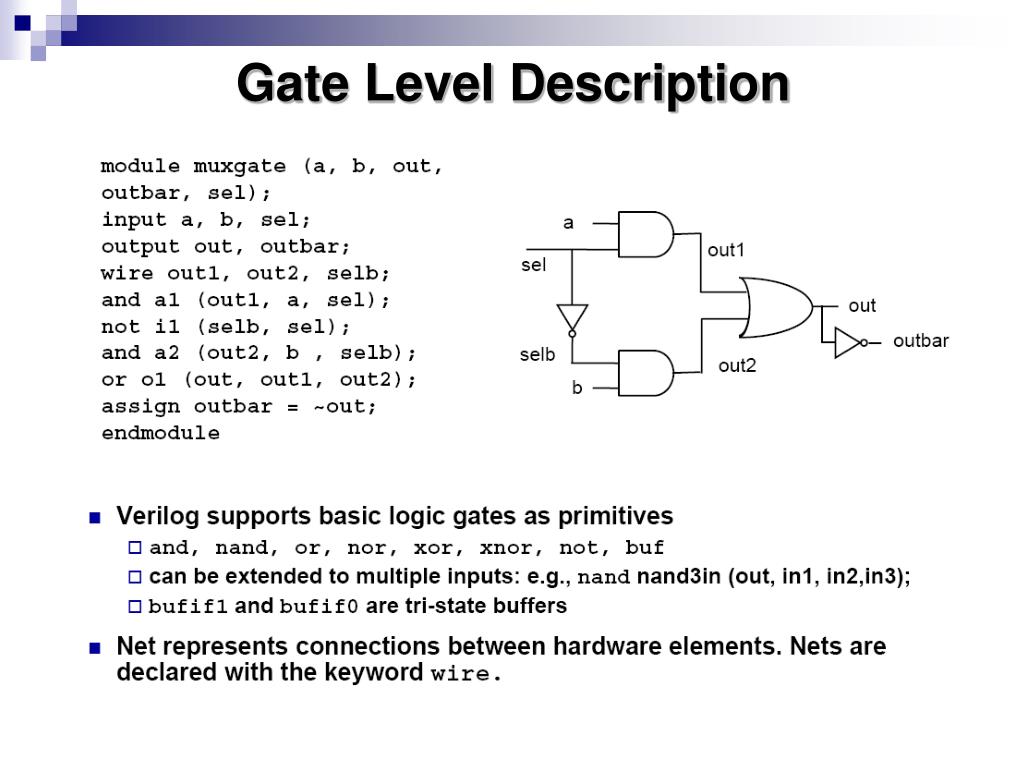

Implementing the Verilog OR gate in your digital designs is straightforward. The syntax for defining an OR gate in Verilog involves specifying the input and output ports. Here is a simple example of an OR gate module:

module or_gate ( input wire A, input wire B, output wire Y ); assign Y = A | B; // OR operation endmodule

In this example, the module named "or_gate" takes two inputs, A and B, and outputs Y, which is the result of the OR operation. The "assign" statement is used to define the logic function, using the pipe operator (|) to represent the OR operation.

What Are the Common Uses of the Verilog OR Gate?

The Verilog OR gate is widely used in various applications, including:

- Data routing in multiplexers

- Control signal generation

- Implementing arithmetic circuits

- Combining multiple sensor inputs

These applications highlight the versatility and importance of the Verilog OR gate in digital design.

How Does the Verilog OR Gate Differ from Other Gates?

While the OR gate is a fundamental logic gate, it is essential to understand how it differs from other gates, such as the AND gate and the NOT gate. Here’s a quick comparison:

Read also:Unveiling The Enchanting Antelope Valley Poppy Reserve A Flower Paradise

| Gate Type | Operation | Output Condition |

|---|---|---|

| OR Gate | A | B | Output is high if at least one input is high |

| AND Gate | A & B | Output is high only if both inputs are high |

| NOT Gate | ~A | Output is the inverse of the input |

Each gate serves a unique purpose, and understanding their differences is crucial for effective circuit design.

What Are Some Advanced Applications of the Verilog OR Gate?

In addition to basic applications, the Verilog OR gate can be employed in more advanced digital systems, including:

- Creating complex control logic in processors

- Designing fault-tolerant systems using redundancy

- Implementing state machines for digital systems

These advanced applications showcase the significance of the Verilog OR gate in modern digital design.

How to Test the Verilog OR Gate Functionality?

Testing the functionality of the Verilog OR gate is crucial to ensure that it operates as intended. A common approach to testing is to create a testbench that simulates various input combinations. Below is an example of a simple testbench for the OR gate:

module testbench; reg A, B; wire Y; or_gate uut (.A(A), .B(B), .Y(Y)); initial begin A = 0; B = 0; #10; // Output should be 0 A = 0; B = 1; #10; // Output should be 1 A = 1; B = 0; #10; // Output should be 1 A = 1; B = 1; #10; // Output should be 1 $finish; // End simulation end endmodule

This testbench initializes the inputs and checks the output over different scenarios, ensuring that the OR gate functions correctly.

Conclusion: Why is the Verilog OR Gate Important?

The Verilog OR gate is a fundamental building block in digital logic design, offering simplicity and versatility for various applications. By understanding its functionality, syntax, and implementation, designers can create more complex circuits and systems. The knowledge gained from mastering the Verilog OR gate serves as a stepping stone toward more advanced digital design concepts, ultimately empowering engineers to innovate and optimize electronic systems.

Article Recommendations